300mm Wafer Nano Fabrication Process (1)

Updated:

Wafer Fabrication Process

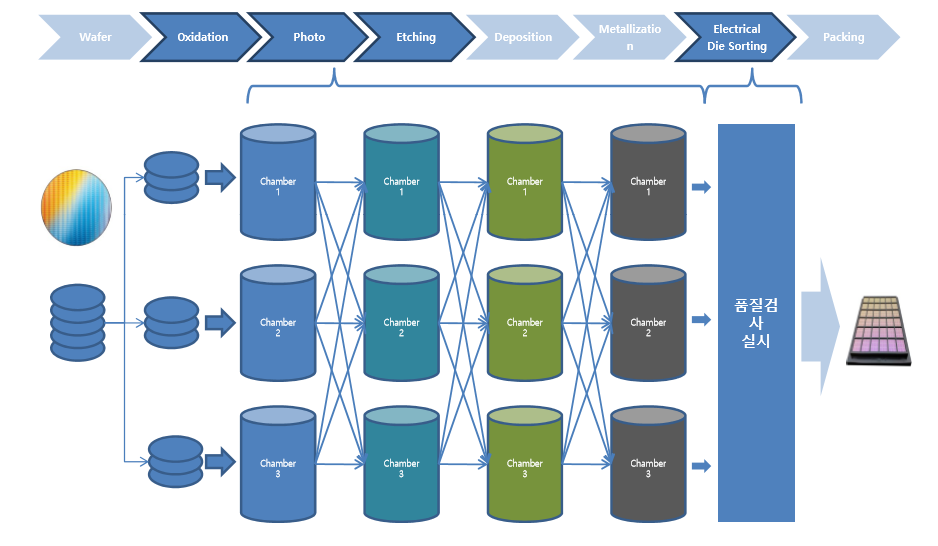

공정 데이터 프로세스

- Wafer : 약 300mm의 disk 형태, 반도체를 제작하는 순도 높은 규소재료

- Wafer Fabs : Wafer를 생산하는 공장, 현재 수집된 데이터는 Fabs에서 발생하는 데이터 중 일부만 추출하여 가져온 것이다.

- Die : Wafer IC 회로에서 발생하는 여러 Chip 들 중 하나, 가장 작은 단위 Unit

- CMOS 소자 제작에 대한 공정 결과 Data를 받아 분석

-

CMOS 에서도 각각 제품에 특성에 맞게 Process가 모두 다르지만, 해당 데이터는 가장 일반적인 Wafer Fabs Process를 가정 하여 분석

- Wafer Fabrication : 총 4단계의 Process에서 발생한 Data로 분석하며, 각 단계별로 넘어갈 때, Wafer가 Process가 같은 3개의 Chamber로 나뉘어 들어감

산화 공정

산화막을 생성하여 Wafer를 보호

- 회로 사이 누설 전류 차단

- 식각공정에서 필요한 부분이 잘못 식각되는 것을 막는 식각 방지막 역할

-

Oxidation 방식

방식 첨가물 반응 속도(상대적) 정확도(상대적) Wet Vapor(수증기) 빠름 정확x Dry Gas(산소 가스) 느림 정확 Dry는 반응 속도가 느려 얇은 막을 형성, Wet은 반응 속도가 빠르고 두꺼운 막을 형성

-

적정 환경

적정 산화막 두께 적정 산화 온도 700nm 이상 750~1200℃ (data : 750 ~ 1100)

포토 공정(Photo Lithography)

Wafer 위에 회로 패턴이 담긴 마스크 상을 빛을 이용해 비춰 회로를 그리는 공정으로 반도체 공정에서 가장 중요한 공정이다.

- 데이터에서는 2개의 파일로 나뉘어 져 있으며, Spin Coat 과정과 Soft Bake 과정이 하나의 파일로 되어있고, Exposure 과정이 다른 하나의 파일로 구성되어 있다.

- 포토 공정 내 8개의 Process

- Vapor Prime : Wafer를 준비하는 단계, Wafer를 증기에 노출시켜 표면을 Hydrophobic(소수성)을 띄도록 만든다. - Wafer에 이물질 제거 및 Resist를 쉽게 흡착 시킬 수 있도록 만든다.

- Spin Coat : Prime Wafer에 액체 Photo Resist 물질을 코팅한다.

- Soft Bake : Coating의 쓰였던 용매를 제거하고 Wafer의 균일성 향상을 위해 Wafer를 굽는 작업

- Alignment and Exposure : Wafer에 감광물질에 빛을 쏘여, Pattern을 새기기 위햐여, 빛이 노출되는 부분을 조절하 는 Mask를 위에 올려, Wafer와 Mask와 Light Source를 정렬하고, 빛을 노출시키는 과정

- Post-Exposure Bake (PEB) : 감광물질이 빛에 노출된 직후, Develop과정 전에 Wafer를 살짝 굽는 작업

- Develop : Photoresist 감광물질에 Pattern이 생성되는 단계로, Spin / Spray / puddle 방법을 이용해, Wafer에 Pattern을 남기는 과정

- Hard Bake : 남아있는 감광물질을 증발시키고, Resist와 wafer사이의 접착을 향상시키는 작업

- Develop Inspect : 품질 검증 및 오류를 수정하는 작업 , Line Critical Dimension 을 확인하여, Transfer 된 구조 간의 거리를 확인한다. 25~55nm 사이로 CD 값이 나와야 적절히 공정이 진행되었다고 판단

- Resolution : Lithography 과정에서 사용되는 중요한 지표로, 얼마나 미세한 Pattern을 구현하는가에 대한 척도

- Lithography에서 Resolution과정이 Critical Dimension을 결정하는 가장 중요한 요인

- Lithography 과정에서 UV Spectrum에 따라 Resolution이 달라짐

- G – Line / H – Line / I – Line

- Exposure : 단위 면적 당 Power x Time => Energy

- Lithography에서 Resolution 수 있는 여러 가지 개선안을 찾는 것이 중요 (SCALPEL / IPL / DESIRE 등 .. )

-

최적 환경

적정 Line_CD(Line Critical Dimension) : Lithography의 결과로 그려진 Wafer의 Line Pattern 간 거리 25nm 이상 55nm 이하

식각 공정

동판화 에칭(Etching) 기법과 비슷한 식각공정

: 식각공정은 식각 반응을 일으키는 물질의 상태에 따라 습식(wet)과 건식(dry)로 나뉩니다. 건식 식각(Dry Etching)은 반응성 기체, 이온 등을 이용해 특정 부위를 제거하는 방법이며, 습식 식각(Wet Etching)은 용액을 이용 화학적인 반응을 통해 식각하는 방법입니다.

Wafer 표면 위에 원하지 않는 물질을 선택적으로 제거하는 단계로 2가지 프로세스가 존재, Dry Etching / Wet Etching (현재 데이터에선, Dry Etching을 사용)

- Dry Etching - 미세공정에 있어서 적합한 Process / 균일성이 좋으며, 매우 우수한 Profile (Etching된 Feature의 Sidewall 모양)

- Gas 형태의 Plasma를 제거하려는 부분에 노출, 물리/화학적 Process가 동시에 진행

- 불소 기반의 Source를 이용해 Plasma형태로 변환 - 첨가물엔 H²와 O²가 존재

- 핵심 Parameter :

- Etching Rate : Process가 진행되는 중, Wafer 표면에 Material이 제거되는 속도

- Etch Uniformity : Etching이 Wafer 표면에서 얼마나 균일하게 일어나는 지 파악

- Etch Selectivity : 다른 Material의 Etching Rate에 비해 Etching 되는 재료의 비율 (동일한 조건에서 한 Film이 다른 Film에 비해 얼마나 빨리 Etching 되는가 나타내는 척도)

- 현재 주어져 있는 시간당 Etching Thickness를 이용해, Etching Rate를 계산하는 것이 중요

증착 공정 (Implantation Process)

Wafer에 얇은 옷을 입히는 공정으로, 이온주입 공정이다.

: 현재 반도체 공정에서는 화학적 기상증착방법(CVD)를 주로 사용하고 있습니다. 화학적 기상증착방법(CVD)는 사용하는 외부 에너지에 따라 열 CVD, 플라즈마 CVD, 광 CVD로 세분화되는데. 특히 플라즈마 CVD는 저온에서 형성이 가능하고 두께 균일도를 조절할 수 있으며 대량 처리가 가능하다는 장점 때문에 가장 많이 이용되고 있습니다.

- Wafer위에 전기적 특성을 부여하는 단계 , 반도체 결정구조에 Dopant (화학 물질에 도입되어 원래의 전기적 또는 광학적 특 성을 변경시키는 미량의 불순물 원소)를 도입하여 전자적 특성을 부여

- 크게 2가지 타입의 공정이 존재, Thermal Diffusion과 Ion Implantation (현재 데이터는 Ion Implantation공정을 진행한 데 이터)

- Thermal Diffusion : 시간과 온도에 따라 Si 격자구조를 통해 Dopant가 이동하며, 전자적 특성이 부여됨

- Ion Implantation : 고전압 이온충격을 통해 Dopant를 주입

- Ion Implantation 물리적인 Process로 기본적으로 화학반응이 없음

- Plasma를 먼저 생성한 뒤, 선택적으로 Ion을 전송하는 방식

- Annealing 과정을 병행하여 진행

- Wafer 기판을 가열하면서, 원자의 격자 (Lattice) 사이에 손상된 부분을 수리 및 효과적인 Dopant 확산

- Furnace Annealing : 800 ~ 1000℃에서 약 30분간 가열, 광범위하게 Dopant를 확산

- Rapid Thermal Annealing (RTA) : 급속 열처리, Ar 또는 N²를 이용해 불필요한 Dopant의 확산을 줄임

- Furnace Annealing을 먼저 진행한뒤, 너무 많은 Dopant를 제어하기 위해, RTA를 실시

품질 검사(EDS 공정)

수율 확인, 불량원인 확인 및 최종 개선

: EDS 공정(Electrical Die Sorting)은 웨이퍼 위에 전자회로를 그리는 FAB 공정과 최종적인 제품의 형태를 갖추는 패키지 공정 사이에 진행됩니다. 즉 전기적 특성 검사 를 통해 개별 칩들이 원하는 품질 수준에 도달했는지를 확인하는 공정입니다.

1) ET Test & WBI (Electrical Test & Wafer Burn In)

2) Pre-Laser (Hot/Cold)

3) Laser Repair & Post Laser

4) Tape Laminate & Back Grinding

5) Inking

자세한 내용 참조 : https://www.samsungsemiconstory.com/201

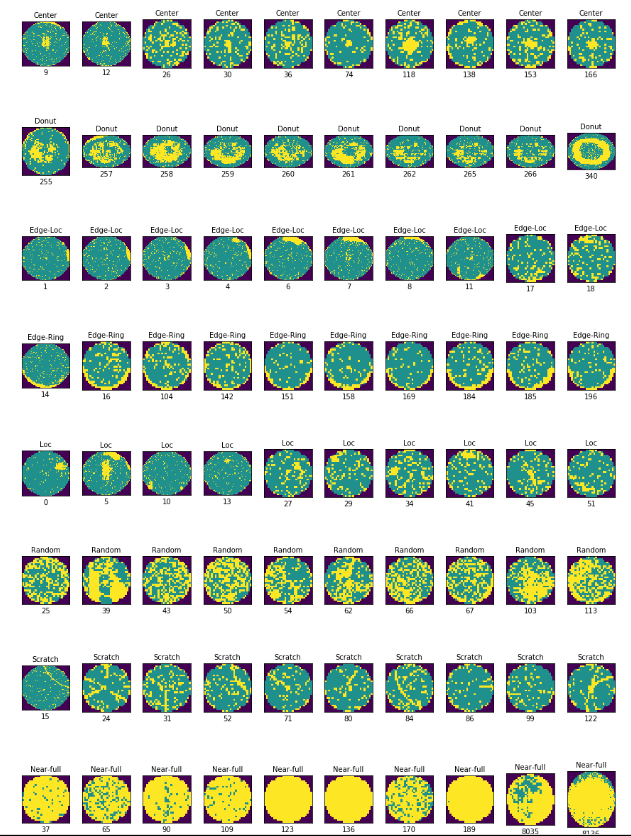

- 에러 종류